ADVANCED CONFIGURABLE SCRYPT MINING ARCHITECTURE SYSTEM (ACSMA)

The Scrypt algorithm was designed to make its implementation in computer systems very poor.

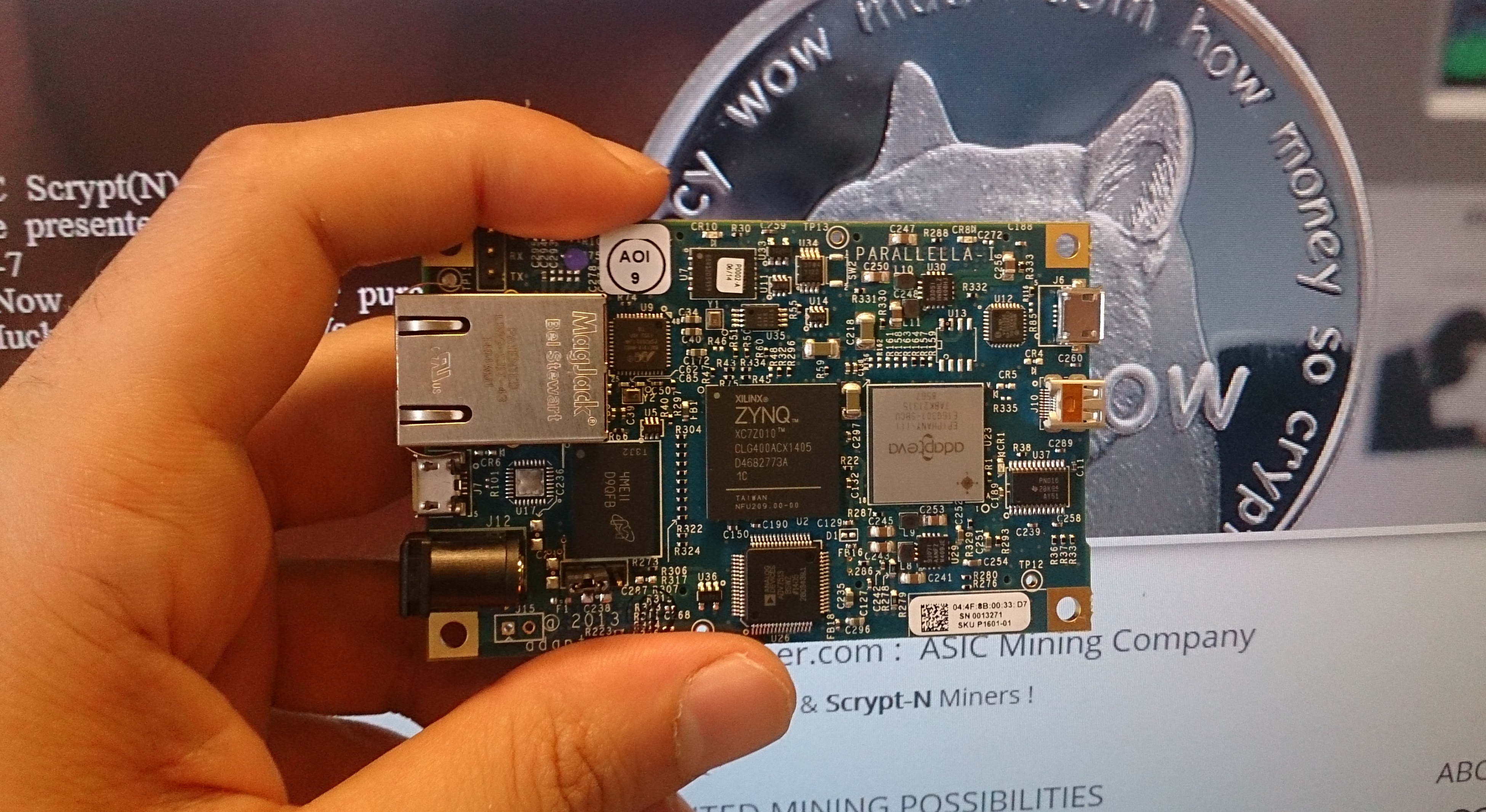

Although, it is better to optimize it in the FPGA systems, it will not be economically feasible via FPGA to obtain high hashing rates. The only viable solution is an ASIC.

We studied the architecture of the algorithm in order to design a very efficient system that works in a typical brute force of a sheer number of mining cores in other mining solutions. To explain the basics it is better to give some figures:

It is well established that one simple hash on a dedicated digital circuit takes around 150,000 clock cycles to execute. We can infer that the shorter time those cycles take, the higher the hashing rate will be. In other words, the circuit hashing rate can be characterized by FC/150k when FC is the clock frequency of such a circuit.

There are only two possible options to increase the hash rate:

Either, increase the hashing rate of the mining solution by increasing the frequency of the circuit, or using a higher number of cores in parallel.

Solution 1:

Increasing the frequency is a part of our purpose. We are considering the 45nm and 22nm technologies. Besides the price factor, we must also consider the thermal issue.

Solution 2:

Mining solution with 2000 to 2500 cores is very high, also it has been considered by other companies.

The number of cores is also another limiting factor.

We chose to look at the architectural side of the multiple mining cores solutions. We realized that, in all cores and at a particular time, only a small fraction of the electronics was being used. Although it is much easier to do silicon copy and paste it on thousands of cores and produce an ASIC very quickly.

This approach is nowhere near optimized, as all of these units cores are not interconnected, neither do they help each other in any way. So billions of expensive transistors are not fully utilized!

This analysis was the basis guideline for the design of ACSMA. To start giving some numbers on the power of ASCMA, we could go back to the original formula for the hashing rate fc/150k.

If we have the possibility to integrate a huge number of hashing cores, let us say 150k cores, the hashing rate of one circuit will be equal to FC.

For a 1 GHz circuit frequency we could obtain 1GHash/S, but this is obviously not possible with the current state of technology. We will need more in excess 50 ASIC chips each with 2500 mining cores with the standard solution.

The architecture of ACSMA addresses the optimization of electronics usage. If the circuit contains 1 billion transistors and all of them are used at the same time ; this optimization is directed to decrease the silicon size of the ACSMA and die ; hence allowing for more equivalent units to increase the size of the embedded high speed rams.

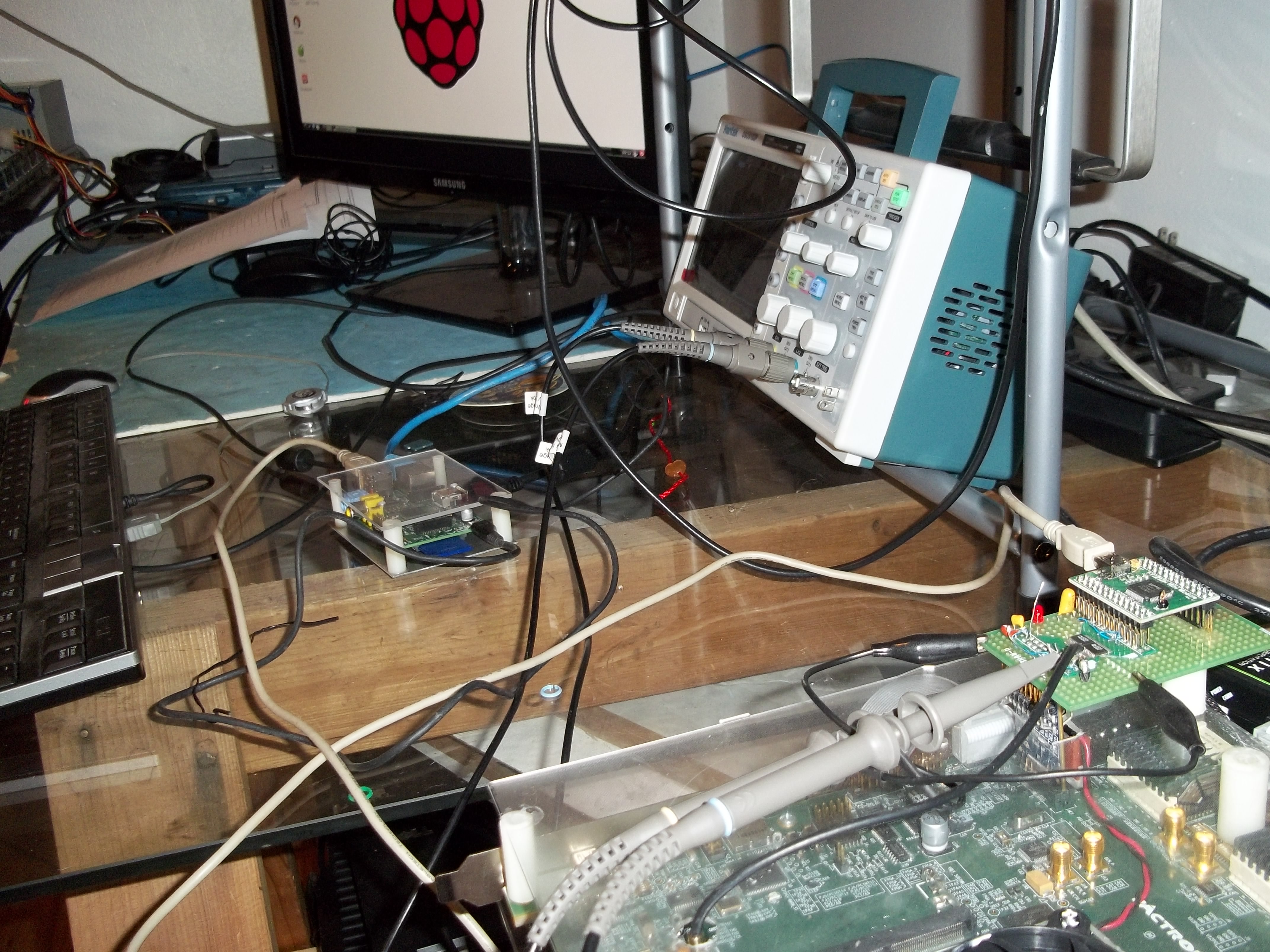

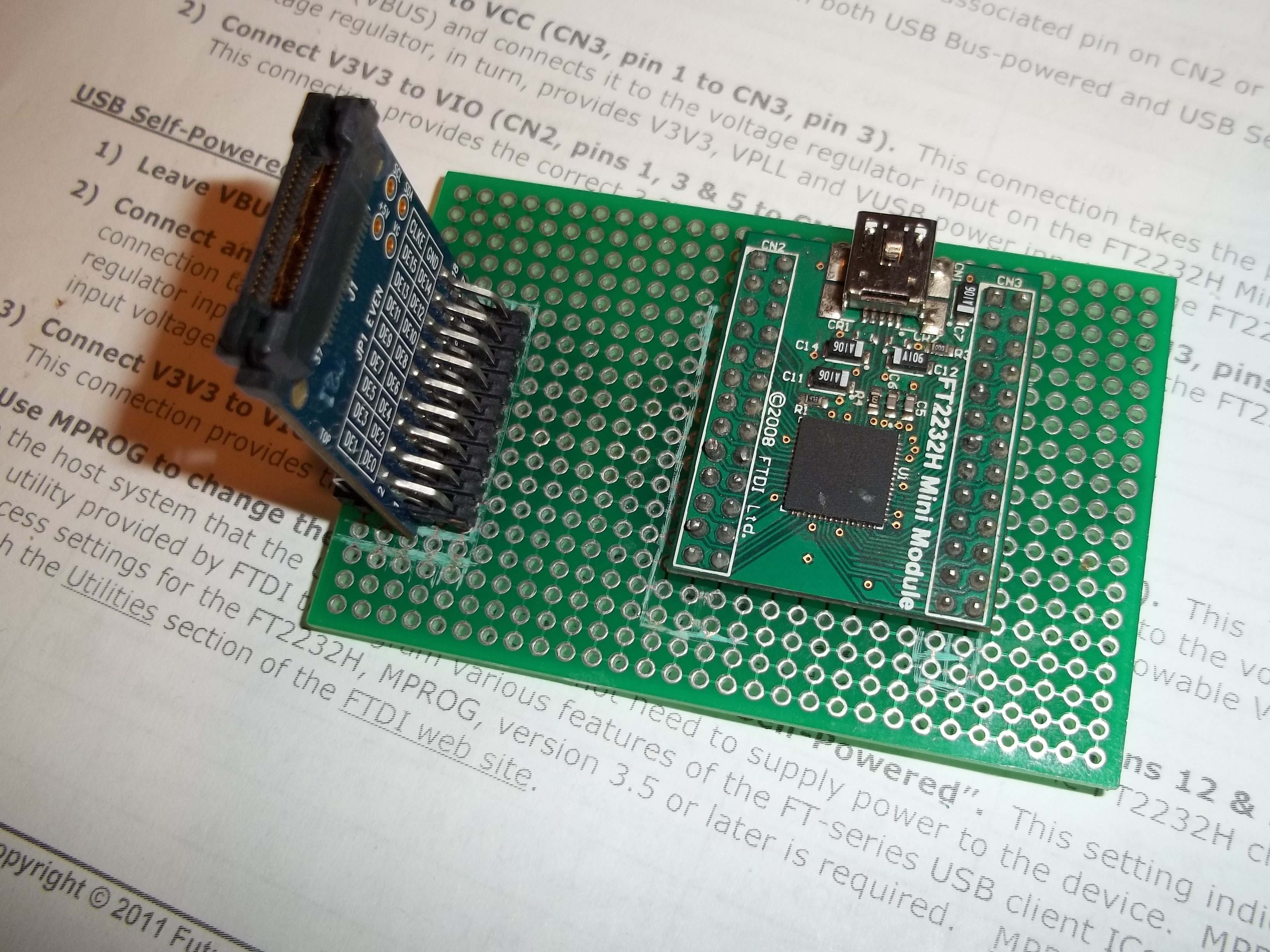

Early in the design of the Litecoin miner we discovered that Nfactor mining was easily possible to add it with few changes. As a matter of fact, ACSMA could also process Bitcoin. This is one of the reasons for the name “Configurable” in ACSMA.

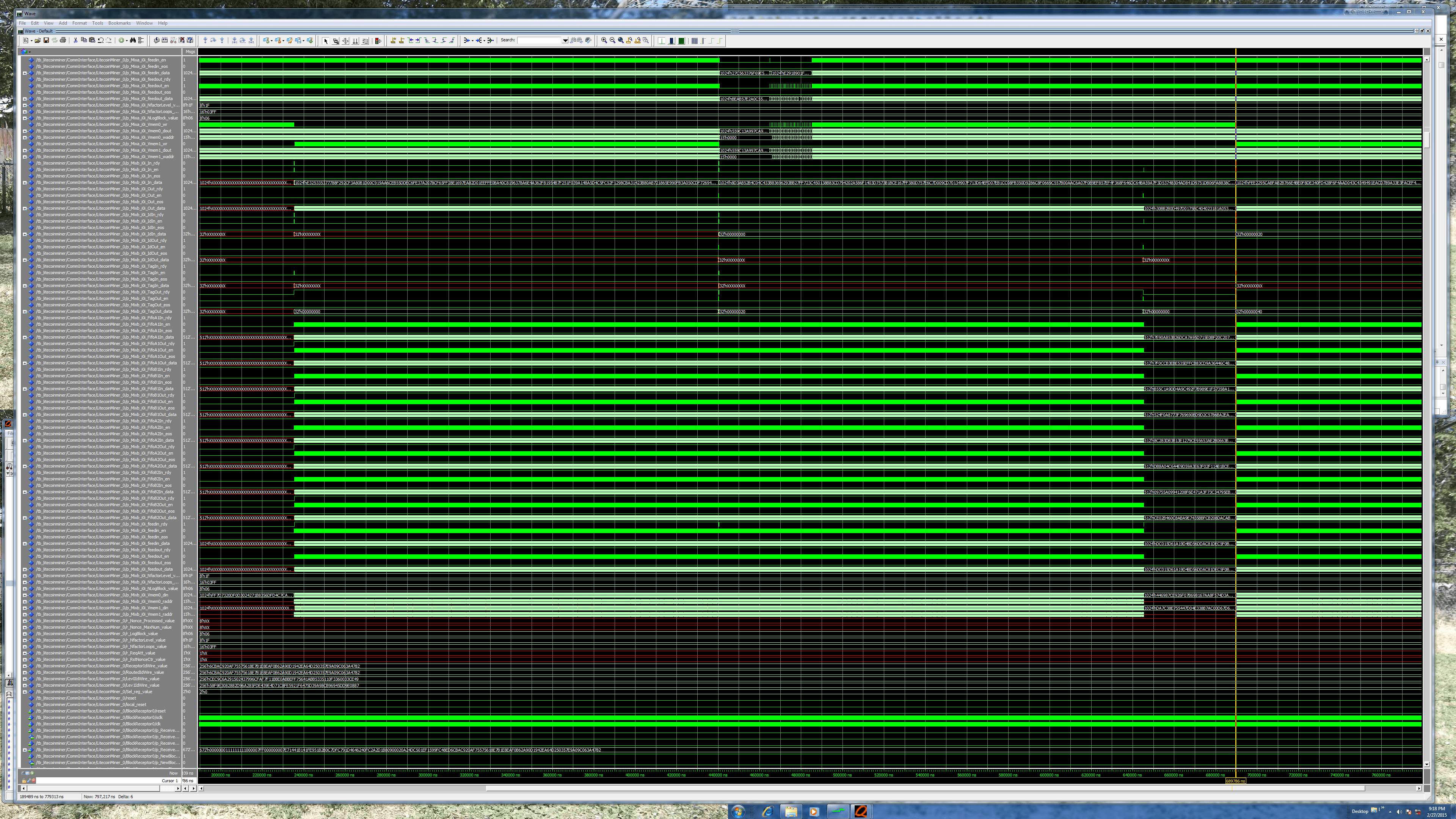

ACSMA has been designed to increase the Hash rate by using an architecture organization. The aim was to produce a HASH per clock cycle. This is not far fetched as it seems. Let’s take the example of the 150k cores architecture. We could run that circuit and produce each 150k cycles a total of 150KHashes (as they are parallel). This is equivalent to 1 Hash per cycle but there is one side effect.

There is a latency of 150kcycles associated, we looked into this and tried to minimize that latency. Although ACSMA cannot escape the curse of the SCRYPT algorithm memory requirements by optimizing the silicon die area to include more memory - it is now possible. ACSMA chips will contain between 2 Gigabits and 4 Gigabits.

ACSMA chips have specialized modules that deal with the memory blocks .The computational power of ACSMA is dependent of the total internal memory given by:

Nu = number of memory units (a minimum of 50 in each chip)

M = Contiguous 1 Megabits memory blocks = 64

Nram = Nu*M: 3.2 Gigabits of total memory

The final value of Nram will be defined in the next design phase, but a minimum of 3.2 Gigabits is part of the design requirements with the ASIC contractor.

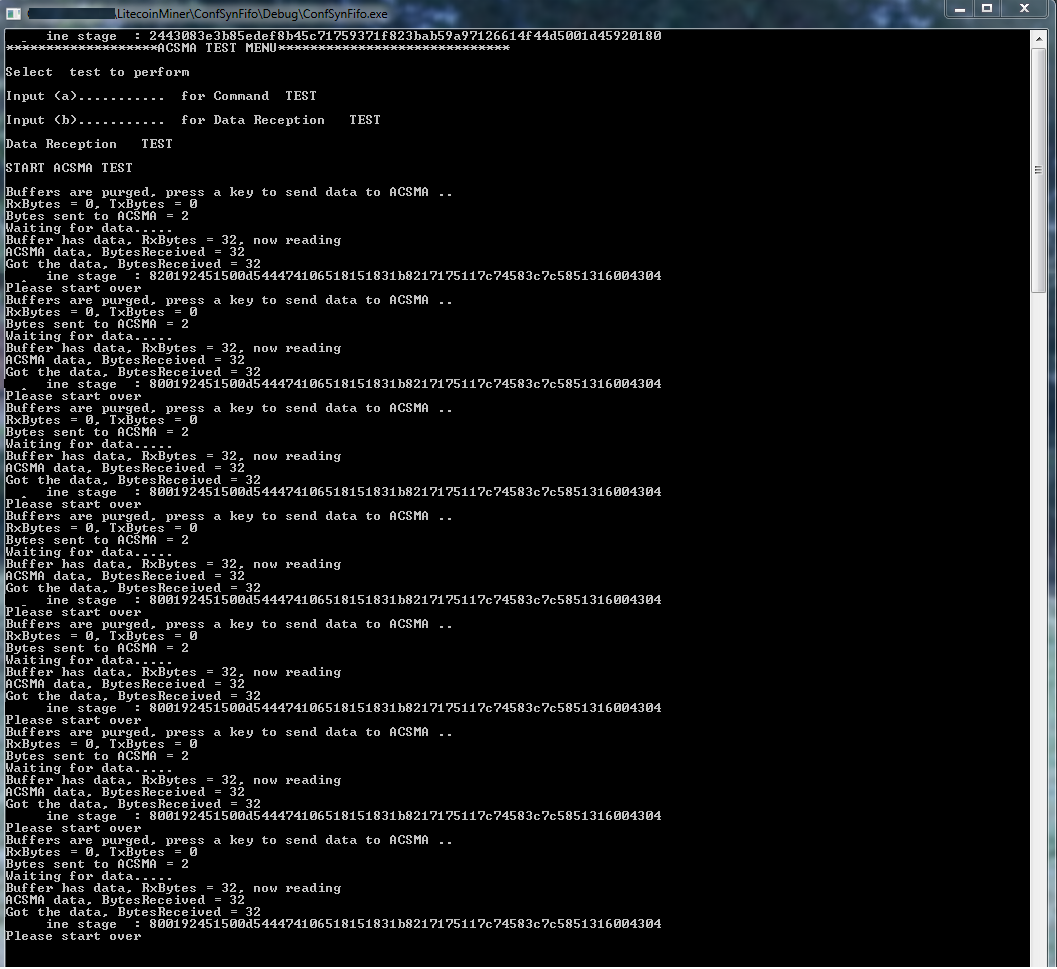

Now, our Scrypt implementation can write each 62 Megabits block in 64K cycles. This defines the Hashing power of ACSMA and it means that one unit inside ACSMA is able to produce an equivalent HASH a little over than 1000 cycles. The total hashing capability needs to be multiplied by Nu the number of memory units.

Fc = 600 MHz

The formula for determining the hashing power for Litecoin N = 10 - With basic values :

Hlcpwr = Nu*(fc/1000) (or 30 Mh/s with basic requirements).

With this setting, 1GH mining rig will require 30 chips or so. Our current API addressing scheme will allow using 256 chips.

Nfactor mining is based on huge memory requirements depending on the value of N

Because memory inside an ASIC is a fixed resource, all we can do is use more memory for each hash.

This will reduce mining hash rate of ACSMA Hnfac depending on the value of N, and it can be stated in terms of Hlcpwr as follows:

Hnfac= Hlcpwr/[2^(Nfac-10)]

Which basically means by using the same memory amount inside ACSMA chips, hashing power is halved every time Nfac is increased ?

Now these numbers are just used as requirements for our basic design .The frequency can be increased, and with the reduction of silicon area with which ACSMA was designed in mind, we will increase the memory blocks and therefore the total hashing power.

We love crypto

Ehsminer Team